Semester

Subject

Year

Tribhuwan University

Institute of Science and Technology

2078

Bachelor Level / First Year / First Semester / Science

B.Sc in Computer Science and Information Technology (CSC116)

(Digital Logic)

Full Marks: 60

Pass Marks: 24

Time: 3 Hours

Candidates are required to give their answers in their own words as for as practicable.

The figures in the margin indicate full marks.

Section A

Long Answers Questions

Attempt any TWO questions.

[2*10=20]

1.

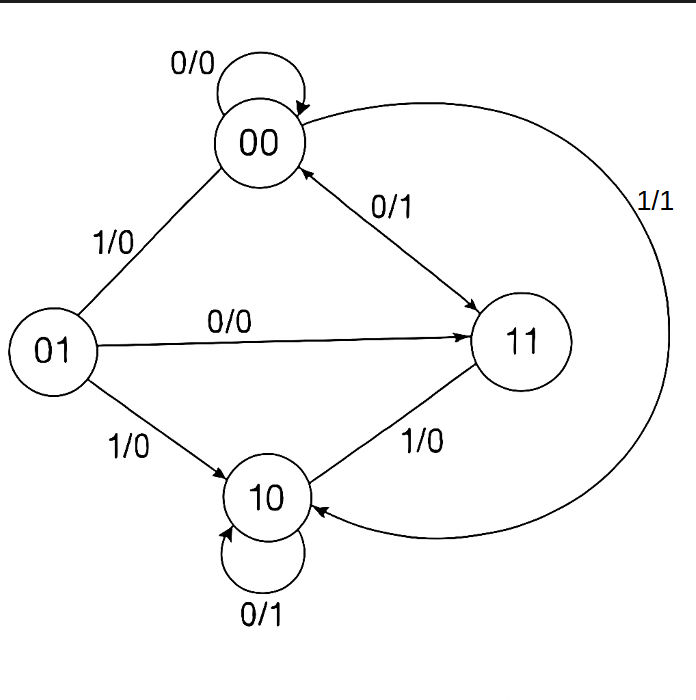

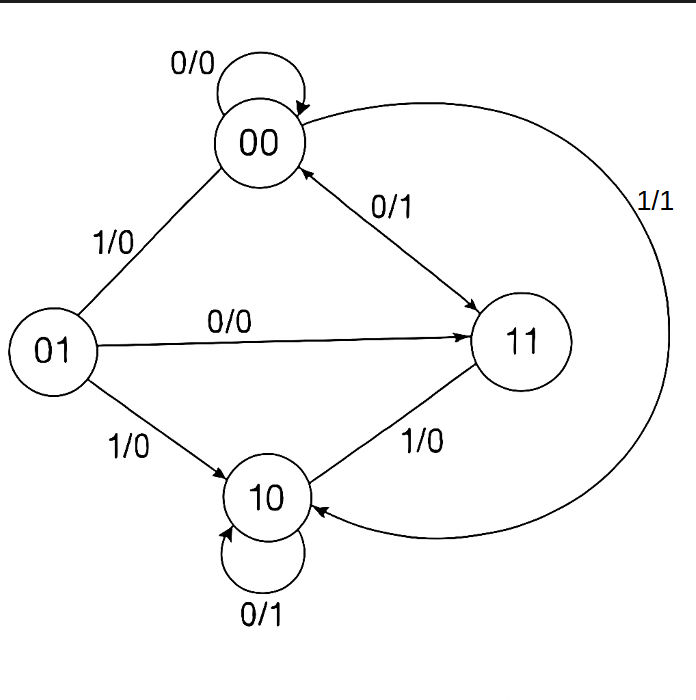

Design the sequential circuit with respect to the following state diagram using J-K Flip flops.  [10]

[10]

2.

Implement F using: a.Multiplexer

b. Decoder c. PLA [4+3+3]

3.

Differentiate between synchronous and asynchronous counter. Design mod-7 synchronous counter using T-flip flop. Show necessary truth tables and k-maps. [10]

Section B

Short Answers Questions

Attempt any Eight questions.

[8*5=40]

4.

Provide one example where shift right operation can be used. Explain parallel-in parallel-out register. [5]

5.

Carry out the following tasks: a. Perform 1's complement subtraction of 10101-100101 b. Represent decimal number 0.125 into its binary form [2.5+2.5]

6.

Derive the Boolean expression for sum and carry of half adder. Draw its combinational circuit. Implement it using only NAND gates. [5]

7.

Express the Boolean function F = x+yz as a product of max-terms. [5]

8.

Minimize the following Boolean function using K-map.

[5]

9.

What are the practical implications of up counter? Explain Binary ripple counter. [5]

10.

Design a combinational circuit with three inputs and one output. The output is 1 when the binary value of the inputs is an odd number. [5]

11.

Differentiate between PLA and PAL. Explain 4-bit magnitude comparator. [5]

12.

Write short notes on (Any Two):

[5]