Semester

Subject

Year

B.Sc Computer Science and Information Technology

Institute of Science and Technology, TU

Digital Logic (CSC116)

Year Asked: 2077, syllabus wise question

Binary Systems

1.

List two major characteristics of digital computer. Represent -6 (negative six) using 8 bits in signed magnitude, signed-1's-complement and signed-2's-complement respectively. Represent decimal number 4673 in a) octal, and b) BCD. [5]

Boolean algebra and Logic Gates

1.

Where is CMOS suitable to use? Define Power dissipation. Show that the positive logic NAND gate is a negative logic NOR gate and vice versa. [5]

Combinational Logic

1.

Design a combinatorial circuit that generates 9's complement of a BCD number. [10]

Combinational Logic with MSI and LSI

1.

Implement the following functions using PLA

[10]

2.

Design a full subtractor circuit with three inputs and two outputs Diff and . The circuit subtracts , where is the input borrow, is the output borrow, and Diff is the difference [5]

3.

Design 4-bit even parity generator. [5]

Registers and Counters

1.

What is the difference between a serial and parallel transfer? Explain how to convert serial data to parallel and parallel data to serial. What type of register is needed? [5]

2.

Explain negative-edge triggered D flip flop with necessary logic diagram and truth table. [5]

3.

Illustrate the use of Binary ripple counter and BCD ripple counter. [5]

Simplification of Boolean Functions

1.

Simplify the following function and implement them with two level NOR gate circuit, [5]

Synchronous and Asynchronous Sequential Logic

1.

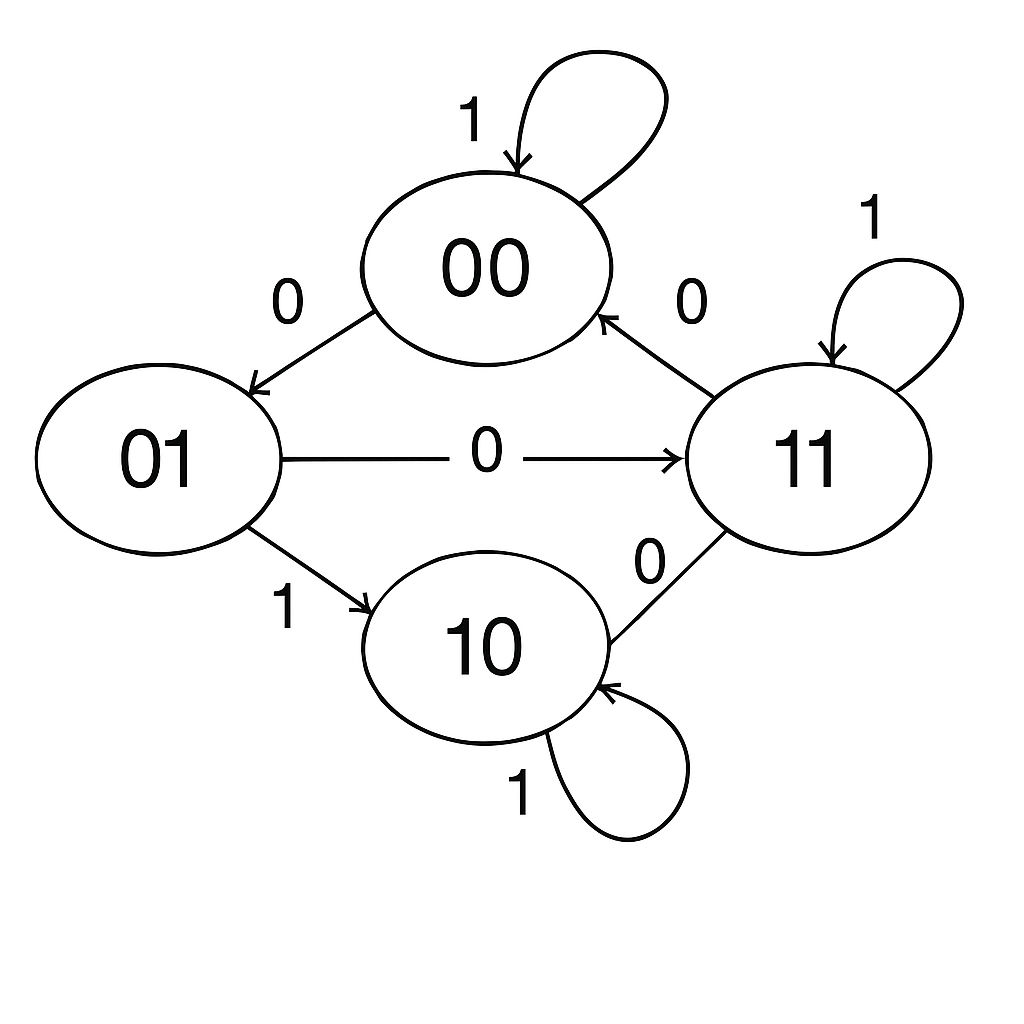

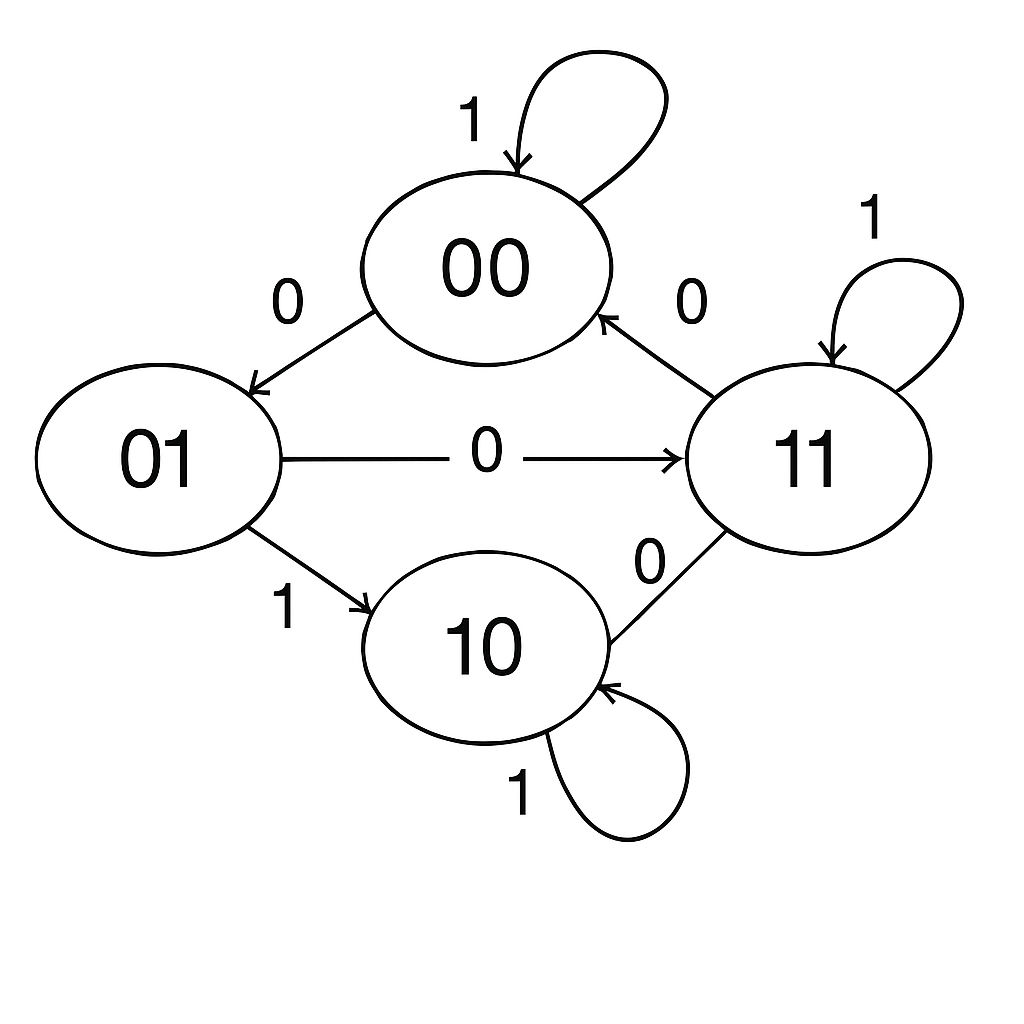

Design sequential circuit specified by the following state diagram using T flip-flops.  [10]

[10]

2.

Write short notes on (Any two):

[5]